## SCH16T-K01 Data Sheet

# 6-DOF XYZ-Axis gyroscope and XYZ-Axis accelerometer with digital SPI interface

#### **Features**

- ±300 °/s calibrated angular rate measurement range.

- ±80 m/s² calibrated acceleration measurement range

- Auxiliary digital accelerometer channel with up to ±260 m/s<sup>2</sup> dynamic range

- Options for output interpolation and decimation

- Angular rate and acceleration low pass filters from 13Hz to 370 Hz cut-off rate

- Data Ready output, timestamp index and SYNC input functions for clock domain synchronization.

- -40...110 °C operating temperature range

- 3.0...3.6 V supply voltage, 1.7...3.6 V I/O supply voltage

- SafeSPI v2.0 interface

- 20-bit and 16-bit output data, selectable via SPI frame

- Extensive self-diagnostic features

- 11.8 mm x 13.4 mm x 2.9 mm (I x w x h) SOIC-24

- Qualification based on AEC-Q100 standard

#### **Applications**

SCH16T series is targeted at applications demanding high performance with tough environmental requirements. Typical applications include:

- Inertial measurement units (IMUs)

- Inertial navigation and positioning

- Machine control and guidance

- Dynamic inclination

- Robotic control and UAVs

#### **Application restriction**

https://www.murata.com/en-global/support/militaryrestriction

#### Overview

The SCH16T is a combined high-performance 3-axis angular rate and 3-axis accelerometer. The angular rate and accelerometer sensor elements are based on Murata's proven capacitive 3D-MEMS technology. Signal processing is done by a single mixed-signal ASIC that provides angular rate and acceleration via a flexible SafeSPI v2.0 compliant digital interface. Sensor elements and ASIC are packaged to pre-molded SOIC 24-pin plastic housing that guarantees reliable operation over the product's lifetime.

The SCH16T is designed, manufactured, and tested for high stability, reliability, and quality requirements. The component has extremely stable output over temperature, humidity, and vibration. The component has several advanced self-diagnostic features, is suitable for SMD mounting and is compatible with RoHS and ELV directives.

## **TABLE OF CONTENTS**

| 1 |              | oduction                                                                  |    |

|---|--------------|---------------------------------------------------------------------------|----|

| 2 |              | duct types and order codes with packing quantity                          |    |

| 3 | •            | ecifications                                                              |    |

|   | 3.1          | Abbreviations                                                             |    |

|   | 3.2          | General specifications                                                    |    |

|   | 3.3          | Absolute maximum ratings                                                  |    |

|   | 3.4          | Performance specifications for gyroscope                                  |    |

|   | 3.5          | Performance specifications for accelerometer                              |    |

|   | 3.6          | Gyroscope typical performance characteristics                             |    |

|   | 3.7          | Accelerometer typical performance characteristics                         |    |

|   | 3.8          | Temperature sensor                                                        |    |

|   | 3.9          | Gyroscope and accelerometer frequency response and filter characteristics |    |

|   | 3.10         | Pin description                                                           |    |

|   | 3.11         | Digital I/O specification                                                 |    |

|   | 3.12<br>3.13 | SPI AC characteristics  Measurement axis and directions                   |    |

|   | 3.13         | Package outline drawing                                                   |    |

|   | 3.14         | PCB footprint                                                             |    |

| 4 |              | neral product description                                                 |    |

|   | 4.1          | Component block diagram                                                   |    |

|   | 4.1          | Accelerometer                                                             |    |

|   | 4.3          | Gyroscope                                                                 |    |

|   | 4.4          | Factory calibration                                                       |    |

| 5 |              | nponent operation, reset and power-up                                     |    |

|   | 5.1          | Component operation                                                       |    |

|   | 5.2          | Internal fault diagnostics                                                |    |

|   | 5.3          | Component output channels                                                 |    |

|   | 5.4          | Solutions for asynchronous clock domains                                  |    |

|   | 5.4.         |                                                                           |    |

|   | 5.4.         | ·                                                                         |    |

|   | 5.4.         | 3 SYNC input pin                                                          | 25 |

|   | 5.4.         | 4 Data ready, DRY                                                         | 26 |

|   | 5.4.         |                                                                           |    |

|   | 5.4.         |                                                                           |    |

|   | 5.4.         |                                                                           |    |

| 6 |              | mponent interfacing                                                       |    |

|   | 6.1          | Safe SPI                                                                  |    |

|   | 6.2          | SPI frame structure                                                       |    |

|   | 6.3          | Multi-slave operation                                                     |    |

|   | 6.4          | SPI frame status bits                                                     | 31 |

|   | 6.5          | Cyclic redundancy check (CRC)                                             | 32 |

|   | 6.5.         |                                                                           |    |

|   | 6.5.         |                                                                           |    |

|   | 6.6          | Operations                                                                |    |

|   | 6.6.         | · ·                                                                       |    |

| , | 6.6.         |                                                                           |    |

| 1 | _            | gister definition                                                         |    |

|   | 7.1          | Register map user guide                                                   |    |

|   | 7.1.         | 1 Value and address formats                                               | 3b |

|   | 7.1.2   | Register map overview                                     | 36 |

|---|---------|-----------------------------------------------------------|----|

|   | 7.2 Ser | nsor data block                                           |    |

|   | 7.2.1   | Example of angular rate data conversion                   | 38 |

|   | 7.2.2   | Example of acceleration data conversion                   | 38 |

|   | 7.2.3   | Example of temperature data conversion                    | 39 |

|   | 7.3 Ser | nsor status block                                         | 39 |

|   | 7.3.1   | Data counters                                             | 40 |

|   | 7.3.2   | Frequency counter / timestamp                             | 40 |

|   | 7.3.3   | Status summary                                            |    |

|   | 7.3.4   | Saturation status summary                                 |    |

|   | 7.3.5   | Common status                                             |    |

|   | 7.3.6   | Gyroscope common status                                   |    |

|   | 7.3.7   | Gyroscope status XYZ                                      |    |

|   | 7.3.8   | Accelerometer status XYZ                                  |    |

|   | 7.3.9   | Additional status registers                               |    |

|   |         | nsor control block                                        |    |

|   | 7.4.1   | Filter settings                                           |    |

|   | 7.4.2   | Dynamic range and decimation                              |    |

|   | 7.4.3   | User interface control                                    |    |

|   | 7.4.4   | Self-test controls                                        |    |

|   | 7.4.5   | Sensor mode control and soft reset                        |    |

|   | 7.4.6   | Whoami, traceability, identification, and spare registers |    |

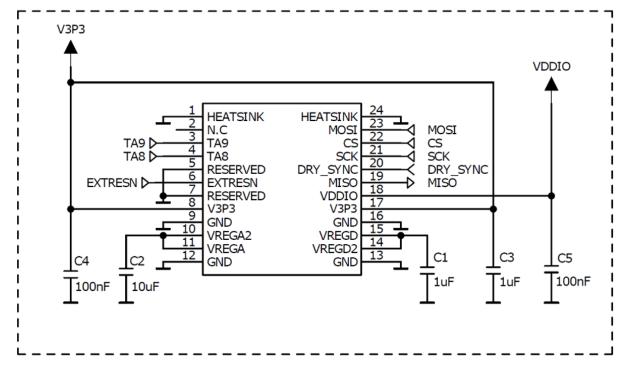

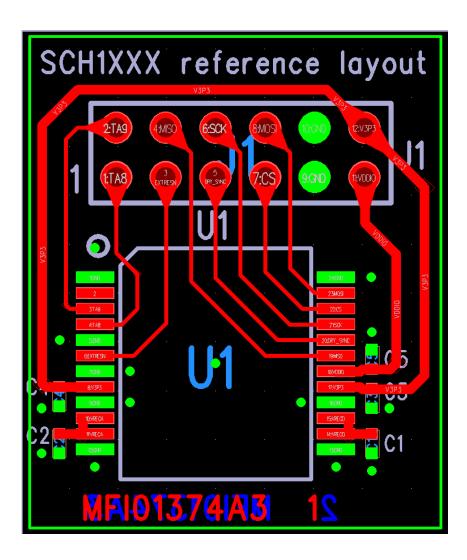

| 8 |         | tion information                                          |    |

|   |         | Dication circuitry and external component characteristics |    |

|   |         | neral application PCB layout                              |    |

| 9 | Assemb  | oly instructions                                          | 53 |

### 1 Introduction

This document contains essential technical information about the SCH16T sensor including specifications, SPI interface descriptions, user-accessible register details, electrical properties, and application information. This document should be used as a reference when designing in the SCH16T component.

## 2 Product types and order codes with packing quantity

Table 1 Product types and order codes

| Product Type   | Description | Packing              | Quantity |

|----------------|-------------|----------------------|----------|

| SCH16T-K01-004 |             | Sample package, Bulk | 4 pcs    |

| SCH16T-K01-1   | -,,         | Tape & Reel          | 100 pcs  |

| SCH16T-K01-10  |             | Tape & Reel          | 1000 pcs |

## 3 Specifications

#### 3.1 Abbreviations

ARS Angular Rate Sensor (gyroscope)

ASIC Application Specific Integrated Circuit

CS Chip Select

DPS Degrees Per Second

DRY Data Ready

F\_PRIM Gyroscope Primary Frequency

FREQ Frequency

Gyro Gyroscope

LPM Low Power Mode

LPF Low-Pass Filter

MCU Microcontroller Unit

MEMS Micro-Electro-Mechanical System

MISO Master In Slave Out MOSI Master Out Slave In

PD Pull Down PU Pull Up

RT Room Temperature

SCK Serial Clock

SPI Serial Peripheral Interface

SYNC Synchronization

Rev. 2

#### 3.2 **General specifications**

Table 2 General specifications for SCH16T series

| Parameter                                               | Min   | Nom                  | Max   | Unit |

|---------------------------------------------------------|-------|----------------------|-------|------|

| Operating Temperature                                   | -40   |                      | 110   | °C   |

| Supply Voltage                                          | 3.0   | 3.3                  | 3.6   | V    |

| Digital I/O supply                                      | 1.7   |                      | 3.6   | V    |

| Total Supply Current                                    | 36    | 41                   | 47    | mA   |

| Low Power Mode current consumption                      |       |                      | 10    | mA   |

| Gyro Primary Frequency, F_PRIM                          | 22.1  | 23.6                 | 25.1  | kHz  |

| Output update rate - Interpolated outputs (F_PRIM x 16) | 353.6 | 377.6                | 401.6 | kHz  |

| Output update rate - Decimated outputs                  |       | 23.6/X <sup>(1</sup> |       | kHz  |

| Turn-on-time (2                                         |       |                      | 250   | ms   |

<sup>1)</sup> Decimation ratio X is selectable from the following options: 2, 4, 8, 16 and 32 2) After voltage supplies are within specification

#### 3.3 **Absolute maximum ratings**

Murata guarantees sensor operation without parameter related damage or functional deviation within these maximum ratings. However, output values may deviate from specification if parameter values are outside limits defined in Performance specifications for gyroscope and Performance specifications for accelerometer. All voltages are related to the potential at GND.

Table 3 Absolute maximum ratings

| Parameter            | Remark                                                  | Min  | Nom        | Max  | Unit |

|----------------------|---------------------------------------------------------|------|------------|------|------|

| Supply voltage       | Supply voltage (pins V3P3, VDDIO)                       | -0.3 |            | 3.63 | V    |

| Voltage at Analog    |                                                         | -0.3 |            | 3.63 | V    |

| input/output pins    |                                                         |      |            |      |      |

| Voltage at Digital   |                                                         | -0.3 |            | 3.63 | V    |

| input/output pins    |                                                         |      |            |      |      |

| Storage Temperature  | Within these maximum ratings no damage to the component | -50  |            | 150  | °C   |

|                      | shall occur in an instant or up to max 24 hours         |      |            |      |      |

| ESD_HBM              | ESD according to Human Body Model (HBM), Q100-002       | 2000 |            |      | V    |

| ESD_CDM center pins  | Center pins                                             | 500  |            |      | V    |

|                      | ESD according to Charged Device Model (CDM), Q100-011   |      |            |      |      |

| ESD_CDM corner pins  | corner pins                                             | 750  |            |      | V    |

|                      | ESD according to Charged Device Model (CDM), Q100-011   |      |            |      |      |

| Ultrasonic agitation | Cleaning, welding, etc.                                 |      | Prohibited |      |      |

#### 3.4 Performance specifications for gyroscope

Table 4 Performance specifications for all measurement axes, supply voltage = 3.3 V and at room temperature unless otherwise specified

| Parameter                                             | Condition                                                                    | Min<br>(-3 σ) | Nom    | Max<br>(+3 σ) | Unit         |

|-------------------------------------------------------|------------------------------------------------------------------------------|---------------|--------|---------------|--------------|

| Measurement range A)                                  | Guaranteed valid specification range, lowest selectable sensitivity setting  | ±300          |        |               | °/s          |

| weasurement range                                     | Guaranteed valid specification range, highest selectable sensitivity setting | ±62.5         |        |               | °/s          |

| Offset <sup>B)</sup>                                  | -40 °C +110 °C                                                               | -0.6          |        | 0.6           | °/s          |

| Offset drift over temperature <sup>C)</sup>           | -40 °C +110 °C                                                               | -0.2          |        | 0.2           | °/s          |

| Offset drift over lifetime D)                         | After HTOL 1000h                                                             | -0.2          |        | 0.2           | °/s          |

| Default sensitivity – 16-bit mode E)                  |                                                                              |               | 100    |               | LSB/(°/s)    |

| Default sensitivity – 20-bit mode E)                  |                                                                              |               | 1600   |               | LSB/(°/s)    |

| Sensitivity drift over temperature F)                 | XY axis, -40 °C +110 °C                                                      | -0.3          |        | 0.3           | %            |

| Sensitivity drift over temperature                    | Z axis, -40 °C +110 °C                                                       | -0.2          |        | 0.2           | %            |

| Sensitivity drift over lifetime <sup>G)</sup>         | After HTOL 1000h                                                             | -0.3          |        | 0.3           | %            |

| Linearity error ±300 °/s H)                           | -40 °C +110 °C                                                               |               | 0.02   | 0.08          | °/s          |

| Noise density                                         |                                                                              |               | 0.0006 |               | (°/s)/√Hz    |

| Angle random walk <sup>I)</sup>                       |                                                                              |               | 0.015  |               | °/√h         |

| Bias instability <sup>J)</sup>                        | Allan variance minimum divided by 0.664                                      |               | 0.5    |               | °/h          |

| Orthogonality error (between rate axes) <sup>K)</sup> | -40 °C +110 °C                                                               | -0.15         |        | 0.15          | %            |

| G-sensitivity <sup>L)</sup>                           | For DC gravity input                                                         |               |        | 0.006         | (°/s)/(m/s²) |

#### Notes:

Rev. 2

<sup>•</sup> Specified Min/Max values contain ±3 sigma variation limits of original test population. Typical values are validation population mean (unless otherwise specified). Min/Max and typical values are not guaranteed, values represent validation population

<sup>Specification is valid after 24 hours from reflow.

Each system design including SCH16T series component must be evaluated by the customer in advance to guarantee proper</sup> functionality during operation.

## Table 5 Gyroscope parameter definitions

| Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A)     | Measurement range is tied to electrical headroom and is selectable from predefined options presented in 7.4.2. Changing electrical headroom affects only signal path sensitivity (up to 4*nominal sensitivity).                                                                                                                                                                                                                                                                                         |

| B)     | Initial offset at Murata production measurement after calibration                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C)     | Offset drift over temperature is determined by ((maximum offset value over temperature) - (minimum offset value over temperature)) / 2 in condition of one temperature sweep in specified temperature range.                                                                                                                                                                                                                                                                                            |

| D)     | Estimated from offset drift during 1000 hours of high temperature operating life (HTOL) test at 125 °C and maximum supply voltages.                                                                                                                                                                                                                                                                                                                                                                     |

| E)     | Default sensitivity used in factory calibration. With this default sensitivity, signal has a typical electrical headroom of ±327.5 °/s.                                                                                                                                                                                                                                                                                                                                                                 |

| F)     | $Sensitivity = \frac{AR_{meas}(\Omega_{max}) - AR_{meas}(\Omega_{min})}{\Omega_{max} - \Omega_{min}}$ Where: $\Omega_{max} = \text{applied angular rate at maximum operating range}$ $\Omega_{min} = \text{applied angular rate at minimum operating range}$ $AR_{meas}(\Omega_n) = \text{measured angular rate at } \Omega_n \text{[LSB]}$ Sensitivity drift over temperature is determined by [(maximum sensitivity value over temperature) - (minimum sensitivity value over temperature)] / 2 *100% |

| G)     | Estimated from sensitivity drift during 1000 hours of high temperature operating life (HTOL) test at 125 °C and maximum supply voltages.                                                                                                                                                                                                                                                                                                                                                                |

| H)     | Linearity error is the residual error remaining after a least-squares linear fit over measurement range. (Best fit linear model)                                                                                                                                                                                                                                                                                                                                                                        |

| I)     | Angle random walk is the white noise term estimated from Allan deviation at tau = 1s                                                                                                                                                                                                                                                                                                                                                                                                                    |

| J)     | Allan variance minimum divided by 0.664. Optimization for SPI duty cycle or sample rate is required to achieve typical Allan variance in table. Device is powered on for four hours before data collection starts to permit full thermal stabilization.                                                                                                                                                                                                                                                 |

| K)     | Rate axes are orthogonal if their intersecting angle is exactly 90°. Orthogonality error is the deviation from 90°.                                                                                                                                                                                                                                                                                                                                                                                     |

| L)     | Angular rate offset sensitivity in respect to orientation in the earth gravitation. Contains 0.004 °/s from Earth's rotation. Can not be extrapolated beyond gravitation.                                                                                                                                                                                                                                                                                                                               |

## 3.5 Performance specifications for accelerometer

Table 6 Performance specifications for all measurement axes, up to  $\pm 80$  m/s<sup>2</sup> measurement range, supply voltage = 3.3 V and at room temperature unless otherwise specified

| Parameter                                            | Condition                                                                    | Min<br>(-3 σ) | Nom  | Max<br>(+3 σ) | Unit                    |

|------------------------------------------------------|------------------------------------------------------------------------------|---------------|------|---------------|-------------------------|

| Measurement range <sup>A)</sup>                      | Guaranteed valid specification range, lowest selectable sensitivity setting  | ±80           |      |               | m/s <sup>2</sup>        |

| weasurement range                                    | Guaranteed valid specification range, highest selectable sensitivity setting | ±15           |      |               | m/s <sup>2</sup>        |

| Offset B)                                            | -40 °C +110 °C                                                               | -0.14         |      | 0.14          | m/s <sup>2</sup>        |

| Offset drift over temperature C)                     | -40 °C +110 °C                                                               | -0.07         |      | 0.07          | m/s <sup>2</sup>        |

| Offset drift over lifetime D)                        | After HTOL 1000h                                                             | -0.05         |      | 0.05          | m/s <sup>2</sup>        |

| Default sensitivity – 16-bit mode E)                 |                                                                              |               | 200  |               | LSB/(m/s <sup>2</sup> ) |

| Default sensitivity – 20-bit mode E)                 |                                                                              |               | 3200 |               | LSB/(m/s <sup>2</sup> ) |

| Sensitivity drift over temperature F)                | -40 °C +110 °C                                                               | -0.15         |      | 0.15          | %                       |

| Sensitivity drift over lifetime G)                   | After HTOL 1000h                                                             | -0.1          |      | 0.1           | %                       |

| Linearity error H)                                   | Full Scale<br>-40 °C +110 °C                                                 |               | 0.06 | 0.15          | m/s <sup>2</sup>        |

| Lineality entities                                   | -1g1 g,<br>-40 °C +110 °C                                                    |               |      | 0.01          | m/s <sup>2</sup>        |

| Noise density                                        |                                                                              |               | 0.8  |               | $(mm/s^2)/\sqrt{Hz}$    |

| Velocity random walk <sup>I)</sup>                   |                                                                              |               | 30   |               | (mm/s)/ $\sqrt{h}$      |

| Bias instability J)                                  | Allan variance minimum divided by 0.664                                      |               | 0.20 |               | mm/s <sup>2</sup>       |

| Orthogonality error (between ACC axes) <sup>K)</sup> | -40 °C +110 °C                                                               | -0.15         |      | 0.15          | %                       |

#### Notes:

- Specified Min/Max values contain ±3 sigma variation limits of original test population. Typical values are validation population mean (unless otherwise specified). Min/Max and typical values are not guaranteed, values represent validation population characteristics

- Specification is valid after 24 hours from reflow.

- Each system design including SCH16T series component must be evaluated by the customer in advance to guarantee proper functionality during operation.

- A factor of 98 can be used when converting m/s² to milli-g. Actual gravity depends on sensor location on Earth.

## Table 7 Accelerometer parameter definitions

| Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A)     | Measurement range is tied to electrical headroom and is selectable from predefined options presented in 7.4.2. Changing electrical headroom affects only signal path sensitivity (up to 4*nominal sensitivity).                                                                                                                                                                                                                                                                                                |

| B)     | Initial offset at Murata production measurement after calibration                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C)     | Offset drift over temperature is determined by ((maximum offset over temperature) - (minimum offset over temperature)) / 2 in condition of one temperature sweep in specified temperature range.                                                                                                                                                                                                                                                                                                               |

| D)     | Estimated from offset drift during 1000 hours of high temperature operating life (HTOL) test at 125 °C and maximum supply voltages.                                                                                                                                                                                                                                                                                                                                                                            |

| E)     | Default sensitivity used in factory calibration. With this default sensitivity, signal has a typical electrical headroom of $\pm 163.4 \text{ m/s}^2$ .                                                                                                                                                                                                                                                                                                                                                        |

| F)     | $Sensitivity = \frac{ACC_{meas}(a_{+1g}) - ACC_{meas}(a_{-1g})}{a_{+1g} - a_{-1g}}$ Where: $a_{+1g} = \text{applied acceleration at +1g (i.e., +1g gravity of manufacturing location)}$ $a_{-1g} = \text{applied acceleration at -1g (i.e., -1g gravity of manufacturing location)}$ $ACC_{meas}(a_n) = \text{measured acceleration at a}_n [LSB]$ Sensitivity drift over temperature is determined by [(maximum sensitivity value over temperature) - (minimum sensitivity value over temperature)] / 2 *100% |

| G)     | Estimated from sensitivity drift during 1000 hours of high temperature operating life (HTOL) test at 125 °C and maximum supply voltages.                                                                                                                                                                                                                                                                                                                                                                       |

| H)     | Linearity error is the residual error remaining after a least-squares linear fit over measurement range. (Best fit linear model)                                                                                                                                                                                                                                                                                                                                                                               |

| I)     | Velocity random walk is the white noise term estimated from Allan deviation at tau = 1s                                                                                                                                                                                                                                                                                                                                                                                                                        |

| J)     | Allan variance minimum divided by 0.664. Optimization for SPI duty cycle or sample rate is required to achieve typical Allan variance in table. Device powered on for four hours before data collection starts to permit full thermal stabilization.                                                                                                                                                                                                                                                           |

| K)     | ACC axes are orthogonal if their intersecting angle is exactly 90°. Orthogonality error is the deviation from 90°.                                                                                                                                                                                                                                                                                                                                                                                             |

Rev. 2

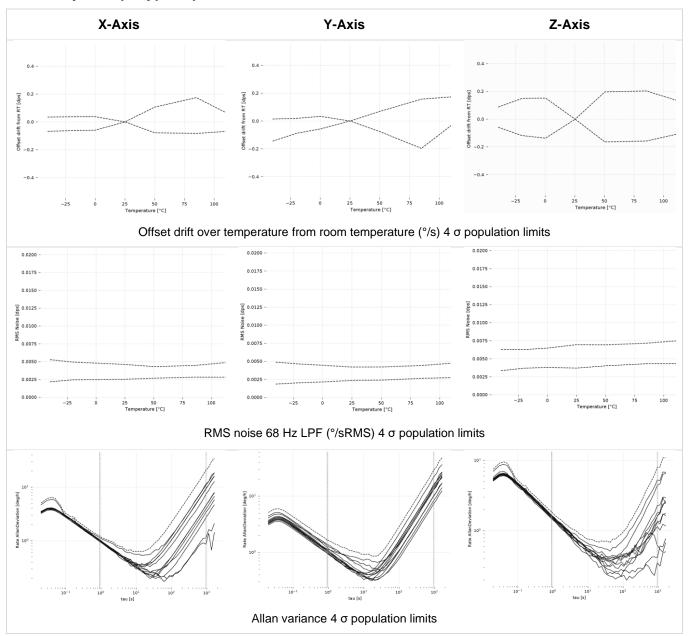

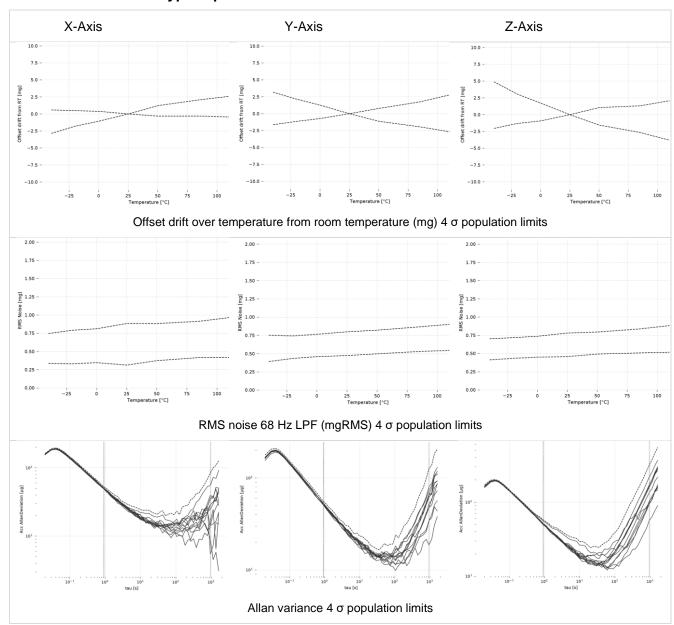

## 3.6 Gyroscope typical performance characteristics

## 3.7 Accelerometer typical performance characteristics

## 3.8 Temperature sensor

Table 8 Temperature sensor performance specification

| Parameter                      | Min | Nom | Max | Unit   |

|--------------------------------|-----|-----|-----|--------|

| Measurement range              | -50 |     | 135 | °C     |

| Temperature signal sensitivity |     | 100 |     | LSB/°C |

| Total Error                    | -15 |     | 15  | °C     |

| Linearity                      | -1  |     | 1   | °C     |

Temperature is converted to °C with following equation:

Temperature [ $^{\circ}$ C] = TEMP / 100, where TEMP is temperature sensor output register content in 2's complement format.

## 3.9 Gyroscope and accelerometer frequency response and filter characteristics

SCH16T Filter characteristics are presented in table below.

Table 9 SCH16T Filter characteristics

| Filter | Title                     | Туре        | Order | Min  | Nom | Max  | Unit |

|--------|---------------------------|-------------|-------|------|-----|------|------|

| LPF0   | Cut-off frequency (-3 dB) | Butterworth | 4     | 63.5 | 68  | 72.5 | Hz   |

|        | Group Delay               |             |       |      |     | 10   | ms   |

|        | Settling time             |             |       |      | 10  | 20   | ms   |

| LPF1   | Cut-off Frequency (-3 dB) | Butterworth | 4     | 28   | 30  | 32   | Hz   |

|        | Group Delay               |             |       |      |     | 16   | ms   |

|        | Settling time             |             |       |      | 25  | 40   | ms   |

| LPF2   | Cut-off Frequency (-3 dB) | Butterworth | 3     | 12.2 | 13  | 13.8 | Hz   |

|        | Group Delay               |             |       |      |     | 35   | ms   |

|        | Settling time             |             |       |      | 65  | 200  | ms   |

| LPF3   | Cut-off Frequency (-3 dB) | Bessel      | 4     | 262  | 280 | 300  | Hz   |

|        | Group Delay               |             |       |      |     | 1.15 | ms   |

|        | Settling time             |             |       |      |     | 5    | ms   |

| LPF4   | Cut-off Frequency (-3 dB) | Bessel      | 3     | 346  | 370 | 394  | Hz   |

|        | Group Delay               |             |       |      |     | 0.78 | ms   |

|        | Settling time             |             |       |      |     | 1.56 | ms   |

| LPF5   | Cut-off Frequency (-3 dB) | Bessel      | 3     | 220  | 235 | 250  | Hz   |

|        | Group Delay               |             |       |      |     | 1.24 | ms   |

|        | Settling time             |             |       |      |     |      | ms   |

| LPF7   | Cut-off Frequency (-3 dB) | None        |       |      |     |      | Hz   |

|        | Group Delay               |             |       |      |     |      | ms   |

|        | Settling time             |             |       |      |     | 0.78 | ms   |

Rev. 2

## 3.10 Pin description

Figure 1 SCH16T pin layout

## Table 10 SCH16T Pin description

| Pin# | Name     | Description                                                                                                                                                                           | Туре    | Voltage<br>Level | Default state/structure |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|-------------------------|

| 1    | HEATSINK | Heatsink connection                                                                                                                                                                   | GND     | 0 V              |                         |

| 2    | Reserved | Leave floating                                                                                                                                                                        | N/A     |                  |                         |

| 3    | TA9      | SPI device selection Address 1 (static). Slave addressing in SafeSPI2. Max four slaves can be addresses by TA9:8. TA on the slave is defined by DVIO logic level at pins TA9 and TA8. | DIN     | 0 V              | 0/PDR <sup>1)</sup>     |

| 4    | TA8      | SPI device selection Address 0 (static). Slave addressing in SafeSPI2. Max four slaves can be addresses by TA9:8. TA on the slave is defined by DVIO logic level at pins TA9 and TA8. | DIN     | 0 V              | 0/PDR <sup>1)</sup>     |

| 5    | Reserved | Connect to GND                                                                                                                                                                        | N/A     |                  |                         |

| 6    | EXTRESN  | External reset input (low active) during normal operation.                                                                                                                            | DIN/AIN | VDDIO            | 1/PUR <sup>1)</sup>     |

| 7    | Reserved | Connect to GND                                                                                                                                                                        | N/A     |                  |                         |

| Pin# | Name     | Description                                                                                                                                                              | Туре     | Voltage<br>Level | Default state/structure |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------------------------|

| 8    | V3P3     | External unregulated inputs for the core supply regulators                                                                                                               | SUPPLY   | 3.3 V            |                         |

| 9    | GND      | Ground                                                                                                                                                                   | GND      | 0 V              |                         |

| 10   | VREGA2   | Regulated core voltage for the analog circuitry. External capacitor connection for positive reference/supply voltage. Connected in PCB.                                  | AIN      | 2.5 V            |                         |

| 11   | VREGA    | Regulated core voltage for the analog circuitry. External capacitor connection for positive reference/supply voltage. Connected in PCB.                                  | AOUT     | 2.5 V            |                         |

| 12   | GND      | Ground                                                                                                                                                                   | GND      | 0 V              |                         |

| 13   | GND      | Ground                                                                                                                                                                   | GND      | 0 V              |                         |

| 14   | VREGD2   | Regulated core voltage for the digital circuitry. External capacitor connection for positive reference/supply voltage. Connected in PCB.                                 | AIN      | 1.5 V            |                         |

| 15   | VREGD    | Regulated core voltage for the digital circuitry. External capacitor connection for positive reference/supply voltage. Connected in PCB.                                 | AOUT     | 1.5 V            |                         |

| 16   | GND      | Ground                                                                                                                                                                   | GND      | 0 V              |                         |

| 17   | V3P3     | External unregulated inputs for the core supply regulators                                                                                                               | SUPPLY   | 3.3 V            |                         |

| 18   | VDDIO    | Digital supply IO                                                                                                                                                        | SUPPLY   | 3.3 V            |                         |

| 19   | MISO     | Master In Slave Out (SPI)                                                                                                                                                | DOUT     | VDDIO            | TRI                     |

| 20   | DRY_SYNC | Sync input (active high) DRY (Data Ready) outputs an interrupt signal for external MCU when the internal output registers (gyroscope + accelerometer) have been updated. | DIN/DOUT | VDDIO            | 0/PDR                   |

| 21   | SCK      | Serial clock (SPI)                                                                                                                                                       | DIN      | VDDIO            | 0/PDR                   |

| 22   | CS       | Chip select (SPI)                                                                                                                                                        | DIN      | VDDIO            | 1/PUR                   |

| 23   | MOSI     | Master Out Slave In (SPI)                                                                                                                                                | DIN      | VDDIO            | 0/PDR                   |

| 24   | HEATSINK | Heatsink connection                                                                                                                                                      | GND      | 0 V              |                         |

|      | 1        | 1                                                                                                                                                                        | 1        | l                | 1                       |

<sup>1)</sup> Strong PD/PU resistance during device reset state, otherwise weak PD/PU.

Rev. 2

## 3.11 Digital I/O specification

Table 11 SPI DC characteristics describes DC characteristics of the SCH16T sensor SPI I/O pins. Current flowing into the circuit has a positive value.

Table 11 SPI DC characteristics

| Title                                                                          | Symbol  | Min     | Max     | Unit |

|--------------------------------------------------------------------------------|---------|---------|---------|------|

| SPI Voltage Level                                                              | VIO     | 1.7     | 3.6     | V    |

| Input High Voltage                                                             | VIH     | 0.7*VIO | VIO     | V    |

| Input Low Voltage                                                              | VIL     | 0       | 0.3*VIO | V    |

| Input Voltage Hysteresis                                                       | VHYST   | 0.1*VIO |         | V    |

| Input/Output Capacitance                                                       | CIO     |         | 10      | pF   |

| Total MISO load capacitance, <wide> range</wide>                               | CLWIDE  | 10      | 100     | pF   |

| Input pull-down resistance, strong (default)                                   | RPD     | 60      | 140     | kOhm |

| Input pull-up resistance, strong (default)                                     | RPU     | 60      | 140     | kOhm |

| Input pull-down/pull-up resistance, weak (option)                              | RPD/RPU | 200     | 400     | kOhm |

| Output leakage current in case MISO is in high impedance (tri-state) condition | ILEAK   | -10     | 10      | μA   |

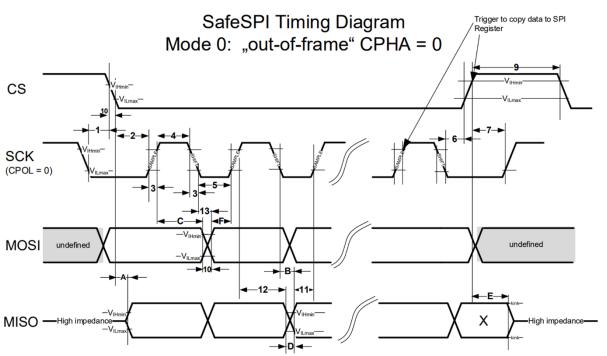

#### 3.12 SPI AC characteristics

Figure 2 Timing diagram of SPI communication (SPI mode 0), CPOL = 0, CPHA = 0

## Table 12 SPI AC electrical characteristics

| Title                     | Remark                                                                                      | Symbol | Min   | Max  | Unit |

|---------------------------|---------------------------------------------------------------------------------------------|--------|-------|------|------|

| SCK Operating             |                                                                                             |        | 0.095 | 10.5 | MHz  |

| Frequency                 |                                                                                             |        |       |      |      |

| MISO data valid time      |                                                                                             | Α      |       | 40   | ns   |

| (CS)                      |                                                                                             |        |       |      |      |

| MISO data valid time      |                                                                                             | В      |       | 32   | ns   |

| (SCK)                     |                                                                                             |        |       |      |      |

| MOSI data hold time       |                                                                                             | С      | 20    |      | ns   |

| MISO rise/fall time       | MISO rise/fall time is not defined during transition between high impedance and active mode | D      | 2     | 9    | ns   |

| MISO data disable lag     | · ·                                                                                         | E      |       | 50   | ns   |

| time                      |                                                                                             |        |       |      |      |

| MOSI data setup time      |                                                                                             | F      | 10    |      | ns   |

| SCK disable lead time     |                                                                                             | 1      | 10    |      | ns   |

| SCK enable lead time      |                                                                                             | 2      | 40    |      | ns   |

| SCK rise and fall time    |                                                                                             | 3      | 2     | 9    |      |

| SCK high time             |                                                                                             | 4      | 37    |      | ns   |

| SCK low time              |                                                                                             | 5      | 37    |      | ns   |

| SCK enable lag time       |                                                                                             | 6      | 20    |      | ns   |

| SCK disable lag time      |                                                                                             | 7      | 10    |      | ns   |

| Sequential transfer delay | In case of MOSI Write commands (RW=1)                                                       | 9      | 750   |      | ns   |

| Sequential transfer delay | In case of MOSI Read commands (RW=0)                                                        | 9      | 450   |      | ns   |

| MOSI rise and fall time   |                                                                                             | 10     | 2     | 9    | ns   |

| MOSI data setup time      | Setup time of MOSI before the rising edge of SCK                                            | 11     | 5     |      | ns   |

| MISO data hold time       |                                                                                             | 12     | Х     |      | ns   |

| MOSI valid time           |                                                                                             | 13     |       | 10   | ns   |

| CS rise and fall time     |                                                                                             | 10     | 2     | 9    | ns   |

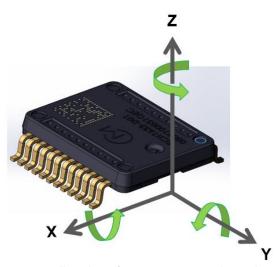

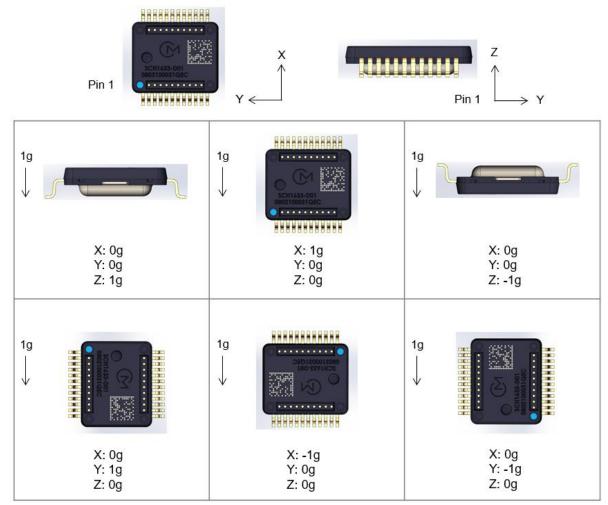

## 3.13 Measurement axis and directions

Figure 3 SCH16T measurement directions for gyroscope and accelerometer

Figure 4 SCH16T accelerometer measurement directions and outputs. 1g indicates direction of gravity. Note: Pin 1 is marked in blue only in this data sheet to emphasize location.

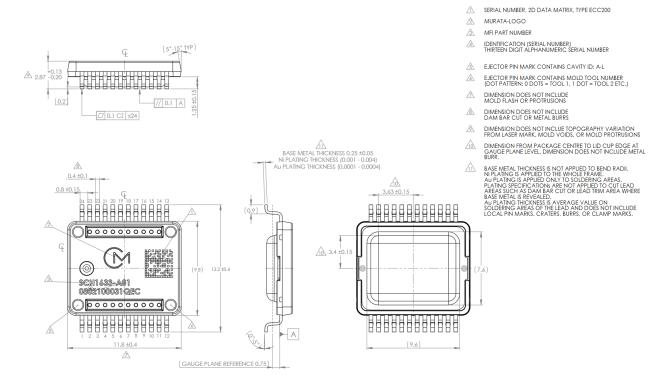

## 3.14 Package outline drawing

Figure 5 The outline of SCH16T package. All dimensions are in millimeters. All angles are in degrees. Tolerances unless otherwise specified according to ISO2768-f. This figure is preliminary and will be updated later.

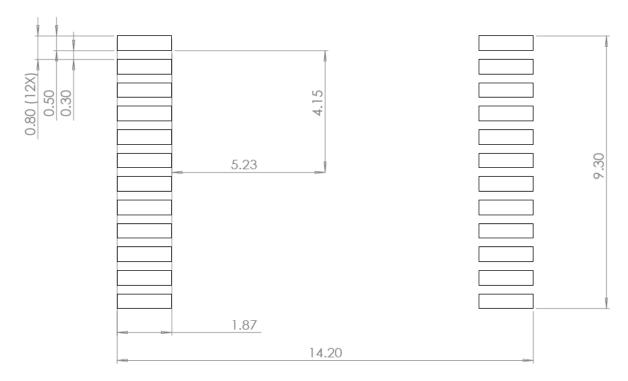

## 3.15 PCB footprint

SCH16T PCB footprint dimensions are presented in the table below.

Figure 6 Recommended PCB pad layout for SCH16T. All dimensions are in millimeters.

This is the end of publicly available document. For full version of this of this data sheet and assembly instructions, please contact Murata.

Murata reserves all rights to modify this document without prior notice.

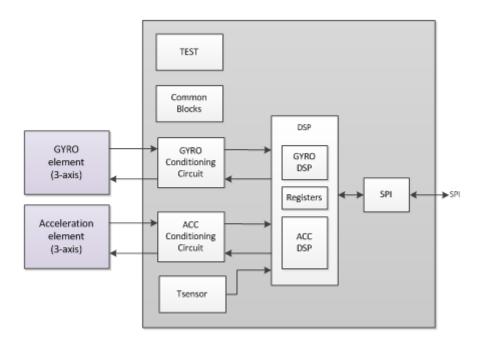

## 4 General product description

## 4.1 Component block diagram

The SCH16T sensor consists of independent acceleration and angular rate sensing elements, and an Application-Specific Integrated Circuit (ASIC) used to sense and control those elements. The angular rate and acceleration sensing elements are manufactured using Murata's proprietary High Aspect Ratio (HAR) 3D-MEMS process, which enables making robust, extremely stable, and low noise capacitive sensors.

Figure 7 SCH16T Component block diagram

#### 4.2 Accelerometer

The acceleration sensing element consists of three acceleration-sensitive masses. Acceleration causes a capacitance change that is converted into a voltage change in the signal conditioning ASIC.

## 4.3 Gyroscope

The angular rate sensing element consists of moving masses that are intentionally exited to in-plane drive motion. Rotation in a sensitive direction causes in-plane (Z) or out-of-plane (XY) movement that can be measured as capacitance change with the signal conditioning ASIC.

#### 4.4 Factory calibration

Sensors are factory calibrated and there is no need for separate calibration in most applications. Factory calibrated parameters include offset, sensitivity, internal fault monitoring signals and cross-axis sensitivity for gyroscope and accelerometer.

CONFIDENTIAL 21 (53)

Sensors are calibrated over temperature in three measurement points at -40 °C, +25 °C, and +110 °C. Offset and sensitivity are calibrated with 2nd order polynomial and cross-axis with linear function. Calibration variables are stored in non-volatile memory during manufacturing and are read automatically during the start-up.

It should be noted that PCB assembly can cause offset errors to the sensor output. If possible, system-level offset calibration (zeroing) after assembly is recommended.

## 5 Component operation, reset and power-up

#### 5.1 Component operation

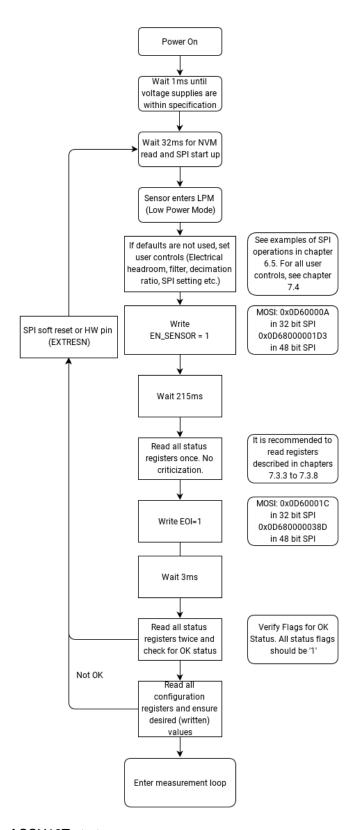

The SCH16T component has an internal power-on reset circuit. After release of EXTRESN and once the power supplies are within the specified range, the component reads configuration and calibration data from the non-volatile memory to volatile registers. After the memory is read, the sensor goes to low power mode and an external SPI command, EN\_SENSOR, is needed to continue to the initialization phase and to start the measurement.

Start-up time is dependent on the low pass filter setting. After power-on or reset (release of EXTRESN or EN\_SENSOR command) the sensor shall be able to provide valid acceleration and angular rate data after the specified power-on start-up time.

SCH16T uses LPF0 (68 Hz) low pass filter setting by default and the filter can be changed by SPI command. SCH16T has extensive internal fault diagnostics to detect possible over range and internal failures. Diagnostic status can be monitored via status bits included in SPI frame and status registers.

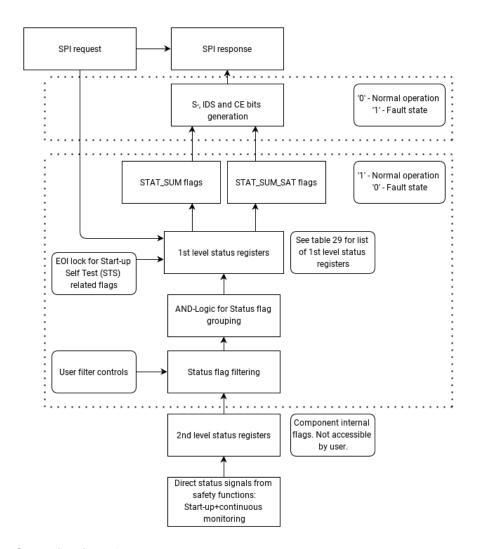

## 5.2 Internal fault diagnostics

During the startup sequence, the sensor performs a series of internal tests that will set various error flags in the sensor status registers. To clear them it is necessary to read the status registers after the start-up sequence is complete. When reading the status registers, the user must consider that the state of status flags is not defined during LPM (Low Power Mode) and the 250 ms wait state after EN SENSOR.

Figure 8 Example of SCH16T start-up sequence

Rev. 2

#### 5.3 Component output channels

The SCH16T series component has several output channels for the user to choose from. The component has two channels for reading gyroscope data and a total of 3 channels for reading acceleration data. Each channel consists of separate X, Y and Z output data registers and each channel and axis has separate status flags. The first gyroscope data channel RATE\_XYZ1 has interpolated output and the second channel RATE\_XYZ2 is for decimated output. The first acceleration channel ACC\_XYZ1 has interpolated output, second channel ACC\_XYZ2 is for decimated output and the third channel is an auxiliary interpolated channel, ACC\_XYZ3. Interpolation and decimation are explained in more detail in 5.4.

The user may choose to utilize multiple channels simultaneously and adjust channel settings separately according to the users' needs. Dynamic range can be individually set for each channel, but filter settings are shared between interpolated and decimated outputs. Different filters within one channel can be applied between X-, Y- and Z-axis, if desired. For example, the user can read ACC\_XYZ1 with nominal ±163.4 m/s² dynamic range and 68 Hz filter, and ACC\_XYZ3 with nominal ±20.48 m/s² dynamic range and 13 Hz filter. The output options are presented in the table below.

Table 13 SCH16T output channel options

| Channel   | Description                                 | Filter setting                                         | Dynamic range setting |

|-----------|---------------------------------------------|--------------------------------------------------------|-----------------------|

| RATE_XYZ1 | Interpolated gyroscope output               | Common for both gyro                                   | RATE_XYZ1 specific    |

| RATE_XYZ2 | Decimated gyroscope output                  | channels, selectable separately for each axis          | RATE_XYZ2<br>specific |

| ACC_XYZ1  | Interpolated accelerometer output           | Common for ACC_XYZ1 and ACC_XYZ2 channels,             | ACC_XYZ1 specific     |

| ACC_XYZ2  | Decimated accelerometer output              | selectable separately for each axis                    | ACC_XYZ2<br>specific  |

| ACC_XYZ3  | Auxiliary interpolated accelerometer output | ACC_XYZ3 specific, selectable separately for each axis | ACC_XYZ3<br>specific  |

### 5.4 Solutions for asynchronous clock domains

Multiple features are implemented to improve synchronization between the product's internal clock and application system clock. While most systems can most likely cope with conventional continuous polling of SPI peripheral, accurate time-domain synchronization can be essential in certain high-performance applications. The table below summarizes the synchronization features.

Table 14 Solutions for asynchronous clock domains

| Feature          | Use case                                      | Value |                                                |

|------------------|-----------------------------------------------|-------|------------------------------------------------|

| Interpolation    | This should be used by default. Interpolation | -     | Minimized sampling jitter                      |

|                  | is applied in outputs RATE_XYZ1,              | -     | Minimized timing difference between channels   |

|                  | ACC_XYZ1, and ACC_XYZ3.                       | -     | No missing samples                             |

| SYNC Input       | Special case. Recommended if there is a       | -     | Synchronization between multiple sensors.      |

|                  | need to sync between multiple SCH16T          | -     | Data can be received with consistent rate even |

|                  | family sensors or if sample time consistency  |       | if host system sampling is affected by         |

|                  | is valued over jitter                         |       | changing load                                  |

| DRY Output (Data | Special case. Recommended only if             | -     | Minimized sampling jitter. With decimated      |

| Ready Interrupt) | decimated, low update rate outputs            |       | outputs, the maximum data jitter depends on    |

|                  | RATE_XYZ2 and ACC_XYZ2 are used.              |       | the decimation ratio and interrupt use removes |

|                  | Decimated outputs are typically used if MCU   |       | this jitter totally.                           |

|                  | bandwidth is limited.                         | -     | No missing samples.                            |

| Data counter     | Special case. Recommended only if Data        | -     | Data counter is index for the component data   |

|                  | Ready is not preferred in application.        |       | output values. The application can monitor     |

|                  |                                               |       | that:                                          |

| Feature                             | Use case                                                                                                                                                                                       | Value |                                                                              |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------|

|                                     |                                                                                                                                                                                                | ,     | odating<br>nted sample has been acquired<br>e sample has not been read twice |

| Data counter with frequency counter | Special case. Recommended if integration operation is performed to sensor data and timing uncertainty or data jitter of the interpolated data do not fulfill the system accuracy requirements. |       | nter together with frequency counter sed for more accurate integration.      |

SYNC and DRY (Data Ready) are implemented on a single hardware pin. Therefore, simultaneous use of these functions is not possible. Controlling the behavior of SYNC and DRY is explained in chapter 7.4.

## 5.4.1 Interpolation

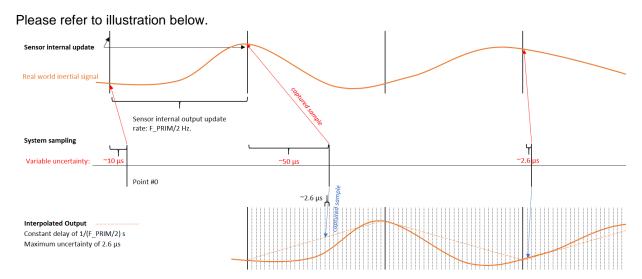

The purpose of interpolation is to minimize time uncertainty (sampling jitter) by increasing artificially the internal sample rate. The natural output data rate of all data outputs is  $F_PRIM/2$ , which is 11.8 kHz with nominal primary frequency. This means that a time-uncertainty between sensor register update and system sampling time could be theoretically anything between 0...85  $\mu$ s.

To minimize this jitter, a fixed interpolation factor of 32 is applied to outputs RATE\_XYZ1, ACC\_XYZ1, and ACC\_XYZ3. With nominal primary frequency it corresponds to a 377.6 kHz refresh rate of register content.

The sample rate is increased by adding a one(1) cycle latency delay to the initial sample. The delay corresponds to the maximum time uncertainty which with nominal primary frequency is 85  $\mu$ s. A linear interpolation is then applied between the initial sample and the new sample, and this interpolation is divided into time segments by the artificially increased update rate 32 x F\_PRIM/2. Time uncertainty is now reduced to the length of this segment, which is max (85  $\mu$ s)/32 = 2.6  $\mu$ s (with nominal primary frequency).

Figure 9 Interpolation (8kHz system sampling rate is used in this illustration)

#### 5.4.2 Decimation

Certain systems need to utilize every available sample and for example acquire samples from all axis at the same time instant. As the natural output data rate with nominal primary frequency is 11.8 kHz, this can create excessive load for the MCU. The purpose of decimation is to decrease the internal update rate to give the host system enough time to read every sample.

During start-up, the user can select a suitable decimation from the options presented in Table 15 Selectable decimation ratios and corresponding ODR. The selected decimation ratio is applied to outputs RATE\_XYZ2 and ACC\_XYZ2.

Table 15 Selectable decimation ratios and corresponding ODR

| Decimation factor | Output data rate | Output data rate with nominal F_PRIM (kHz) |

|-------------------|------------------|--------------------------------------------|

| 1                 | F_PRIM/2         | 11.8                                       |

| 2                 | F_PRIM/4         | 5.9                                        |

| 4                 | F_PRIM/8         | 2.95                                       |

| 8                 | F_PRIM/16        | 1.475                                      |

| 16                | F PRIM/32        | 0.7375                                     |

Drawback of decimation is that sampling jitter is increased with the same ratio as the decimation factor. With nominal primary frequency and decimation ratio of 16, the sampling jitter will be up to 85  $\mu$ s x 16 = 1.36 ms. This means that sample age can be anything between 0 and 1.36 ms. To address this issue, the user can combine decimation with the data ready function. Data ready is explained in chapter 5.4.4.

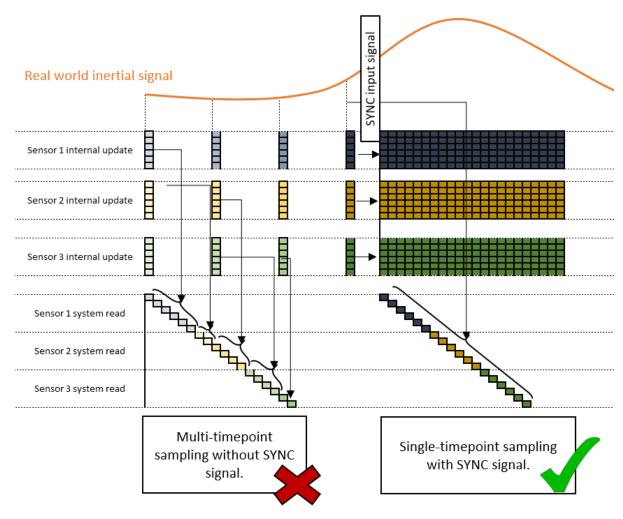

#### 5.4.3 SYNC input pin

Certain systems with high-performance requirements may benefit from use of multiple SCH16T components. Depending on application SPI master clock conditions, the read operation of multiple parallel sensors can take longer than sensor internal register update period if individual MISO line is not used for each component. As a result of this, samples are being acquired from different time instants for each parallel sensor. In certain real-world inputs, this can lead to a significant apparent disagreement of sensors, as different time-instants are being sampled.

To mitigate this issue, SYNC input pin has been implemented. When the master issues SYNC signal to all sensors in the system, the sensors' internal updates for RATE\_XYZ1/2 and ACC\_XYZ1/2/3 are frozen until SYNC pin is set LOW, or after time out period set by CTRL\_SYNC\_TOC\_TH time-out counter. This allows enough time for the master to read all sensor data from a single time instant. CTRL\_SYNC\_TOC\_TH is user-selectable with typical values ranging from 1.2 ms to 11.6 ms. Please refer to chapter 0 for user controls.

SYNC is only feasible on interpolated outputs RATE\_XYZ1 and ACC\_XYZ1/3. With decimated outputs and a decimation factor of 2 or above, most masters should have enough time to read the output registers before they are updated again.

SYNC can be beneficial also to ensure that all 6-axis data is captured at the same time instant. With very low SPI master clocks, it can occur that even a single sensor will update its internal registers during the slow read operation. In this case, different axis data could represent different time instant. SYNC can also help in situations where system load is high, and sampling can not be performed with a consistent frequency.

Please refer to illustration below.

Figure 10 Illustration of SYNC usage when 3 slave sensors are read by single a master

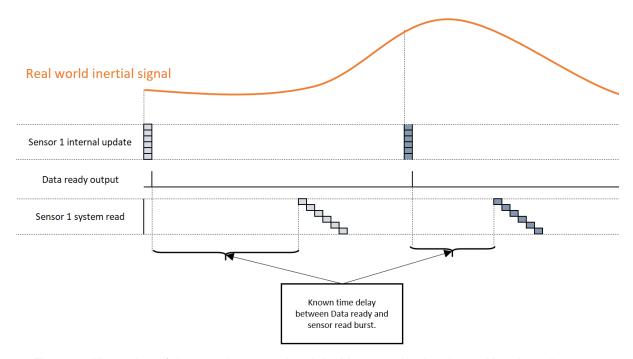

#### 5.4.4 Data ready, DRY

In some system implementations, it may be that the rate at which the host processor can read the peripherals is limited. In these cases, to ensure that the host has enough time to read without signal aliasing it is beneficial to use decimated outputs with suitable decimation factor. When the sensor update rate is lowered by decimation, sampling jitter becomes more of an issue. As explained in chapter 5.4.1, worst case sampling jitter can be up to 85 µs with decimation factor of 1. When decimation factor is increased, the worst-case sampling jitter is increased accordingly.

In case jitter minimization is critical in application, user should use the data ready output pin (DRY\_SYNC). When all sensor output channels have been updated, the data ready triggers a rising edge to indicate that the samples were generated. This rising edge can be used as a direct interrupt to start sensor read operation, or the host can take note of the data ready signal and ensure that the data is read in a burst before the next expected sensor internal update. This way the system can ensure that no samples are missed, and no samples are being read twice.

Please refer to illustration below.

Figure 11 Illustration of data ready output signal. In this example, data is read in a burst between sensor internal updates.

#### 5.4.5 Data counter

Data counter is supported for decimated outputs RATE\_XYZ2 and ACC\_XYZ2. Value of data counter is increased by one when a new sample is available from corresponding RATE/ACC channel. It can be understood as an index for the data output values. Using the data counter, the user can monitor that every wanted sample has been acquired and that the same sample has not been read twice. When using 48-bit SPI protocol, 4-bit data counter value is included in MISO response frame. Data counter can be also used in 32-bit mode by reading DCNT\_RATE and DCNT\_ACC register values via SPI command. Register locations are described in chapter 7.3.

#### 5.4.6 Frequency counter

Using frequency counter, user can acquire accurate clock information from component internal MCLK via SPI. The value of frequency counter register is increased by one with every 16<sup>th</sup> rising edge of master clock.

#### 5.4.7 Calculating exact time stamp

The data counter value can be combined with the frequency counter value to calculate the exact time stamp of a sample when the MCU clock of the host system is used as reference. This combination is recommended if integration operations are performed to sensor data and timing uncertainty or data jitter of the interpolated data do not fulfill system accuracy requirements.

## 6 Component interfacing

#### 6.1 Safe SPI

Product supports Safe SPI v2.0 protocol to transfer data between SPI master and registers of SCH16T ASIC. The product always operates as a slave device in master-slave operation mode. 3-wire SPI connection cannot be used. Communication between master and slave is done with pins described below in Table 16 SPI interface pins.

Table 16 SPI interface pins

| SPI interface pin | Description              | Communication direction |

|-------------------|--------------------------|-------------------------|

| CS                | Chip Select (active low) | MCU to ASIC             |

| SCK               | Serial Clock             | MCU to ASIC             |

| MOSI              | Master Out Slave In      | MCU to ASIC             |

| MISO              | Master In Slave Out      | ASIC to MCU             |

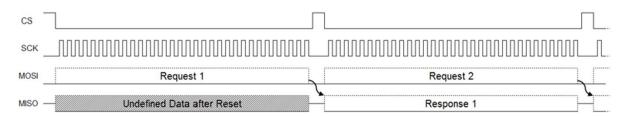

SPI communication uses out-of-frame protocol, so each transfer has two phases. The first phase contains the SPI command (request) and the data (response) of the previous command. The second phase contains the next request and the response to the request of the first phase, see Figure 12. The first response after reset is undefined and shall be discarded.

Figure 12 SPI protocol example

Product SPI block implements two different SPI protocol types. Both protocol types can be used during operation by defining the SPI frame bit length.

- SafeSPI2 32-bit frame, SPI32BF.

- SafeSPI2 48-bit frame, SPI48BF.

SPI block does not implement the complete SafeSPI v2.0 specification. Summary of supported features can be seen in table below. For Safe SPI standard, please refer to <a href="https://www.SafeSPI.org">www.SafeSPI.org</a>

Table 17 SCH16T supported features of SafeSPI v2.0

| Supported feature                       | Description                                                                                          |

|-----------------------------------------|------------------------------------------------------------------------------------------------------|

| <48/32oof>                              | Block receives and transmits 32-bit and 48-bit Out-of-frame SPI frames. In-frame protocols are not   |

|                                         | supported.                                                                                           |

| <frtyp></frtyp>                         | MOSI frame width is defined by received frame length. Frame is effective only if width is 32-bits or |

|                                         | 48-bits and the CRC is valid.                                                                        |

| <selbitwidthbyadr></selbitwidthbyadr>   | Next MISO frame width is decided by <frtyp></frtyp>                                                  |

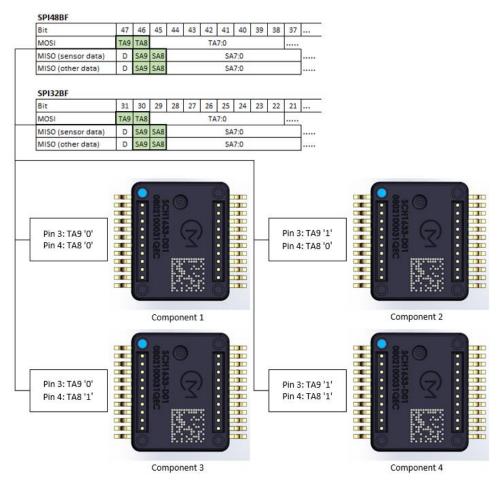

| <sel4slavebyadrpin></sel4slavebyadrpin> | Two MSB address bits can be used to select one of four slaves when one CS signal pin is in use.      |

|                                         | Slave compares the two MSBs to a reference value defined by two input pins.                          |

| <sel4slavebyadrnvm></sel4slavebyadrnvm> | Two MSB address bits can be used to select one of four slaves when one CS signal pin is in use.      |

|                                         | Slave compares the two MSBs to a reference value defined by a NVM programmed value. Factory          |

|                                         | use only.                                                                                            |

| <fixedsensorframe></fixedsensorframe>   | Frame content is well defined and fixed.                                                             |

| <clwide></clwide>                       | Wide range for "total signal load capacitance"                                                       |

| <dcnt></dcnt>                           | Block updates a wrapping 4-bit sample counter each time new sensor data is generated.                |

| <ids></ids>                             | Internal Data Status field includes additional status information for sensor data.                   |

| <cap></cap>                             | Not implemented and replaced with fixed value.                                                       |

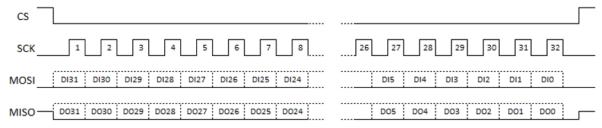

The SPI transmission is always started with the CS falling edge and terminated with the CS rising edge. The data is captured on the SCK's rising edge (MOSI line) and it is propagated on the SCK's falling edge (MISO line). This equals to SPI Mode 0 (CPOL = 0 and CPHA = 0), an example with 32-bit frame can be seen in Figure 13 SPI frame format example (32-bit).

Figure 13 SPI frame format example (32-bit)

#### 6.2 SPI frame structure

SPI Frame format is explained in figure below and Table 18 SPI bit definitions

| SPI48BF            |    |    |    |    |      |      |     |    |    |    |    |     |    |     |    |       |      |    |    |      |     |      |      |     |     |     |     |     |      |      |    |    |    |    |    |    |    |   |   |   |   |   |   |     |   |   |   |   |

|--------------------|----|----|----|----|------|------|-----|----|----|----|----|-----|----|-----|----|-------|------|----|----|------|-----|------|------|-----|-----|-----|-----|-----|------|------|----|----|----|----|----|----|----|---|---|---|---|---|---|-----|---|---|---|---|

| Bit                | 47 | 46 | 45 | 44 | 43   | 42   | 41  | 40 | 39 | 38 | 37 | 36  | 35 | 34  | 33 | 32 3: | 1 30 | 29 | 28 | 27 2 | 6 2 | 5 24 | 4 23 | 3 2 | 2 2 | 1 2 | 0 1 | 19  | 18   | 17   | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3   | 2 | 2 | 1 | 0 |

| MOSI               |    |    |    |    | TA 9 | 9:0  |     |    |    |    | RW | 0   | FT |     |    | Al    | E    |    |    |      |     |      |      |     |     |     |     | DA  | ATAI | 19:  | )  |    |    |    |    |    |    |   |   |   |   |   | С | RC8 |   |   |   |   |